Introduction

In the realm of system design, challenges such as shrinking technology nodes and the need for swift Time to Market (TTM) responses are ever-present. To address these challenges and ensure adaptability to various configurations, the Universal Verification Methodology (UVM) provides a robust solution known as the Register Abstraction Layer (RAL). In this article, we delve into the intricacies of the UVM Register Model, exploring its usage and applications.

Understanding UVM RAL

The UVM RAL serves as a high-level, object-oriented abstraction layer designed for efficient access to design registers. As systems become more generic to cater to diverse configurations, the number of registers increases significantly. UVM RAL manages register access and provides a flexible model that can seamlessly transition from block level to system level verification.

Key Features of UVM RAL

Configurability: The RAL model is fully configurable, accommodating different design scenarios.

Register Attributes Support: It supports various register attributes such as Read/Write, Read-Only, Write-Only, and more.

Dual Access Paths: Frontdoor and backdoor paths facilitate register access.

Compatibility with Multiple Buses: The same RAL model can be accessed by multiple buses.

Abstraction Flexibility: The abstraction nature allows the model's usage at both block and system levels.

Built-in Comparison Method: UVM RAL provides a common API for updating both design and RAL model registers, ensuring consistency.

Hierarchical Structure of UVM RAL

The UVM RAL model is organized into three hierarchical levels:

uvm_reg_block: The topmost hierarchy containing instances of registers (uvm_reg) or other uvm_reg_block components.

uvm_reg: Represents individual registers within the design, with each register potentially having one or more uvm_reg_field components.

uvm_reg_field: Represents the fields of a register.

Check this video on an example that shows one of the ways to access DUT registers with the UVM RAL Model. - https://verificationguide.com/uvm-ral-example/uvm-ral-example-dma/

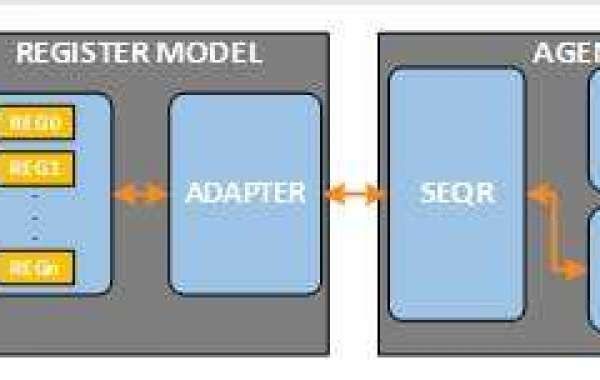

RAL Register Map and Adapter Implementation

Integration of the RAL model involves the implementation of the adapter class. This class includes essential conversion functions, bus2reg() and reg2bus(), responsible for translating bus sequence items into uvm_reg_bus_op (known to RAL model) and vice versa. Adapter classes are bus-specific, requiring a dedicated adapter for each bus accessing the same RAL model.

Example Code:

// Code snippet for reference on adapter class implementationUVM Memory Implementation

UVM extends support for memory implementation within the RAL model, introducing uvm_mem. Similar to uvm_reg, uvm_mem mimics memory within the design. Burst read/write operations are a notable advantage of this memory implementation.

Example Code:

// Code snippet demonstrating memory implementation inside the RAL modelUVM Predictor Models

The UVM RAL model incorporates a self-checking mechanism for registers. Three prediction approaches are available:

Implicit Prediction: Enabled by calling

set_auto_predict(1), predicting values with every write/read operation.Explicit Prediction: Involves creating, configuring, and connecting a

uvm_reg_predictorclass, ensuring the UVM register model stays updated based on actual data.Passive Prediction: Useful when read/write operations bypass the register model, predicting values based on bus interface observations.

Register Coverage in UVM RAL

UVM RAL provides APIs for sampling user-defined covergroups. To enable register prediction, the user must override the sample() method of uvm_reg or uvm_reg_block classes.

Example Code:

// Code snippet illustrating covergroup implementation in UVM RALUVM RAL Pre-defined Sequences

The UVM package offers a set of ready-made sequences for testing register functionality. Sequences cover aspects like reset value checks, bit-bashing, access via different paths, memory operations, shared access, and more.

Example Sequences:

uvm_reg_hw_reset_seq: Checks reset values of each register.uvm_reg_bit_bash_seq: Sequentially writes 1's and 0's to each register bit.uvm_reg_access_seq: Tests register functionality with frontdoor and backdoor access.

Conclusion

In conclusion, UVM RAL emerges as a powerful abstraction layer, simplifying the verification of design registers and memories. Its hierarchical structure, support for memory operations, predictor models, coverage sampling, and pre-defined sequences make it a highly recommended approach for register verification in UVM-based testbenches. By leveraging the organized flexibility provided by UVM RAL, designers can enhance the efficiency and accuracy of their register verification processes.