Hardware verification is a critical phase in the design cycle, ensuring that complex chips and systems operate as intended. Universal Verification Methodology (UVM) has revolutionized the process, offering a standardized framework for creating robust verification environments. Among its powerful features, UVM Register Abstraction stands out as a key element, transforming the way engineers test and validate hardware designs. In this technical blog, we'll explore the intricacies of UVM Register Abstraction, the role of UVM Register Models, and the advantages they bring to the UVM Register Layer.

The Essence of UVM Register Abstraction

At the heart of UVM Register Abstraction lies the need for simplifying the interaction with hardware registers. In the world of hardware design, registers serve as data storage elements, controlling and monitoring different aspects of a chip's functionality. UVM Register Abstraction eases the process of accessing and manipulating these registers within a verification environment.

UVM Register Models: The Blueprint

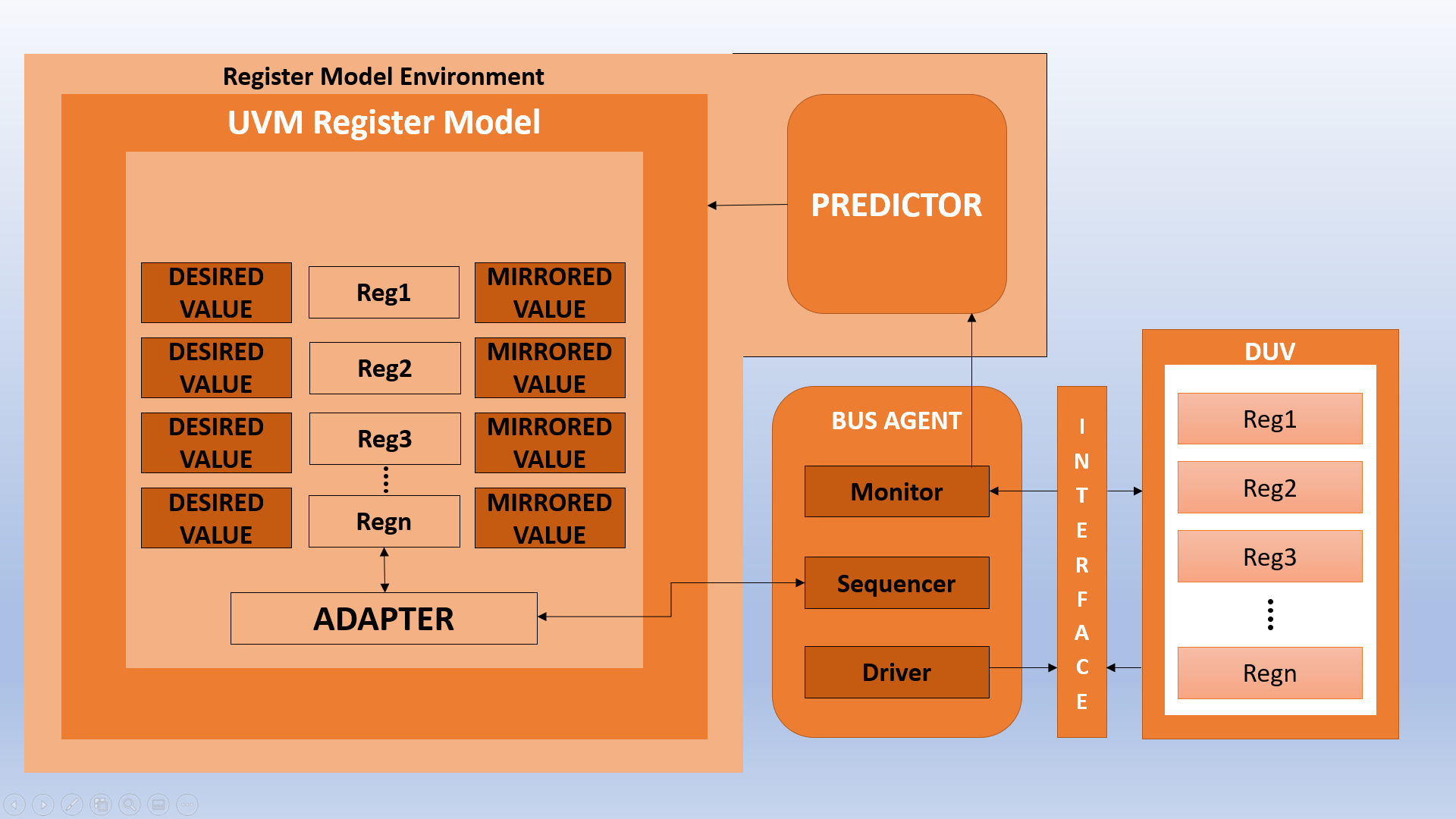

UVM Register Models serve as the blueprint for the registers in your design. They abstract the low-level hardware details, presenting an interface that verification engineers can readily work with. These models encapsulate essential characteristics of registers, including their fields, access mechanisms, and behaviors. As a result, they facilitate the creation of test scenarios that closely resemble real-world usage, all while maintaining the simplicity of high-level abstraction.

The Role of the UVM Register Layer

The UVM Register Layer is where the rubber meets the road. It acts as the intermediary between the verification environment and the hardware design. Here's how it plays a crucial role:

Register Configuration: The UVM Register Layer allows you to configure register settings. Engineers can define characteristics such as reset values, access permissions, and field properties.

Register Access: Engineers can interact with registers just as if they were dealing with the actual hardware. This streamlined access enables a deeper understanding of how registers function and react to various inputs.

Regmodel-based Testing: UVM Register Models enable regmodel-based testing. This approach allows verification engineers to create tests based on the desired register functionality, promoting reusability and reducing the need for manual test scenario development.

Coverage and Automation: Achieving comprehensive coverage is paramount in verification. The UVM Register Layer simplifies this process by automating the collection of coverage metrics, ensuring that no register functionality remains untested.

Maximizing Verification Efficiency with UVM Register Abstraction

The benefits of UVM Register Abstraction are profound. By employing UVM Register Models and leveraging the UVM Register Layer, hardware engineers can streamline verification efforts. This not only accelerates the verification process but also enhances the quality and reliability of hardware designs.

Reduced Debugging Effort: With UVM Register Models, debugging becomes more straightforward. Errors can be traced back to specific registers and their behaviors, saving time and effort.

Enhanced Reusability: UVM Register Models are reusable components. Once created, they can be employed across different projects and testbenches, promoting a consistent and efficient verification process.

Improved Collaboration: A standardized UVM Register Abstraction ensures that the entire verification team, from RTL designers to testbench developers, speaks the same language. This alignment fosters smoother collaboration and better communication.

Faster Time to Market: Time is of the essence in the highly competitive hardware industry. UVM Register Abstraction accelerates the verification phase, contributing to shorter development cycles and faster time-to-market.

Challenges and Considerations

While UVM Register Abstraction offers numerous advantages, it's not without challenges. Engineers must carefully design and manage UVM Register Models to ensure accuracy and completeness. Additionally, the dynamic nature of UVM Register Abstraction requires proper synchronization and coordination in a multi-threaded simulation environment.

1. Register Model Design and Management

One of the primary challenges in UVM Register Abstraction is designing and managing UVM Register Models. These models must accurately represent the registers in the hardware design, including their fields, access mechanisms, and behaviors. Any inaccuracies in the model can lead to flawed test scenarios and missed bugs. Therefore, meticulous attention to detail is essential during the model creation process.

To overcome this challenge, engineers often rely on the design specification of the hardware registers. These specifications serve as the basis for creating UVM Register Models, ensuring that they faithfully mimic the behavior of the actual registers. Furthermore, maintaining consistency between the register specification and the UVM Register Models is crucial, as any discrepancies can lead to misinterpretations and errors in the verification process.

2. Multi-threaded Simulation Environment

Modern hardware designs often involve multiple processes and parallel execution, which can complicate the verification process. In a multi-threaded simulation environment, synchronization and coordination become critical to avoid race conditions and ensure accurate results.

UVM Register Abstraction, with its support for multi-threaded simulations, helps address this challenge. However, engineers must still be vigilant in managing concurrent access to registers. Proper synchronization mechanisms, such as semaphores or locks, must be employed to prevent conflicts when multiple threads attempt to access the same registers simultaneously.

3. Register Configuration Complexity

Register configuration in UVM Register Abstraction can be complex, as it involves defining various register properties, such as reset values, access permissions, and field properties. Managing these configurations efficiently and accurately is essential for a successful verification process.

One way to address this challenge is to create a standardized and well-documented configuration process. By defining clear guidelines for configuring registers, engineers can ensure consistency across the entire verification team. Additionally, automation tools can be employed to streamline the configuration process, reducing the likelihood of human error.

4. Maintaining Coverage Metrics

Achieving comprehensive coverage is a fundamental goal in hardware verification. It ensures that all aspects of the design have been adequately tested, reducing the risk of undetected bugs. UVM Register Abstraction offers automated coverage collection, but maintaining and interpreting coverage metrics can still be challenging.

To overcome this challenge, engineers should establish clear coverage goals and regularly review coverage reports. Additionally, they can employ coverage-driven verification methodologies to focus testing efforts on areas with low coverage. Automation tools can aid in tracking and visualizing coverage metrics, making it easier to identify areas that require additional testing.

Real-world Benefits of UVM Register Abstraction

Despite the challenges, the advantages of UVM Register Abstraction are substantial and have a real impact on hardware verification efficiency and reliability.

1. Time and Effort Savings

One of the most significant benefits of UVM Register Abstraction is the time and effort savings it provides. By abstracting the low-level hardware details and automating many verification tasks, engineers can develop testbenches and test scenarios more rapidly. The ability to reuse UVM Register Models across projects further accelerates the verification process, reducing the need to recreate the same functionality for different designs.

Additionally, debugging becomes more efficient with UVM Register Models. Errors can be traced back to specific registers and their behaviors, simplifying the troubleshooting process and reducing debugging time.

2. Enhanced Reusability

UVM Register Models are reusable components that can be applied to various projects and testbenches. This reusability promotes consistency in the verification process and reduces the effort required to develop new test scenarios. Engineers can build on existing UVM Register Models, adding or modifying functionality as needed for different designs.

The ability to reuse UVM Register Models not only saves time but also contributes to a higher level of confidence in the verification process. As models are refined and improved over time, they become increasingly reliable, enhancing the overall quality of verification.

3. Improved Collaboration

In a typical hardware verification team, engineers from various disciplines collaborate to ensure the correctness of a design. UVM Register Abstraction facilitates this collaboration by providing a standardized interface for registers and their behaviors. This means that RTL designers, testbench developers, and verification engineers all speak the same language when discussing register functionality.

A common understanding of registers and their behavior simplifies communication, reduces misunderstandings, and streamlines collaboration. It also makes it easier to transition between different roles within the verification team, as engineers can leverage their knowledge of UVM Register Models in various capacities.

4. Faster Time to Market

The hardware industry is highly competitive, and time to market is a critical factor in the success of a product. UVM Register Abstraction contributes to shorter development cycles by expediting the verification phase. With efficient testbench development, rapid debugging, and comprehensive coverage, engineers can more confidently sign off on designs and move them into production.

Moreover, the use of UVM Register Models ensures that thorough testing has been conducted, reducing the likelihood of post-production defects and costly revisions. This, in turn, accelerates the time to market and positions a product for success in a fast-paced industry.

Best Practices for UVM Register Abstraction

To harness the full potential of UVM Register Abstraction and its associated components—UVM Register Models and the UVM Register Layer—engineers should follow best practices:

1. Start with Accurate Register Specifications: The foundation of UVM Register Models is the register specification. Begin with an accurate and comprehensive specification to ensure that the models faithfully represent the hardware design.

2. Maintain Consistency: Continuously update UVM Register Models to align with any changes in the hardware specification. Consistency between the specification and the models is vital for accurate testing.

3. Establish Clear Configuration Procedures: Create well-documented procedures for configuring registers. Standardized configuration processes reduce the risk of errors and ensure that all registers are correctly set up for testing.

4. Prioritize Coverage-Driven Verification: Focus on coverage-driven verification to ensure that all aspects of the design are adequately tested. Regularly review coverage metrics and use automation tools to identify areas that require additional testing.

5. Employ Multi-threaded Simulation Techniques: In multi-threaded simulation environments, employ synchronization mechanisms, such as semaphores or locks, to manage concurrent access to registers. This reduces the risk of race conditions and ensures accurate results.

Conclusion

In the realm of hardware verification, UVM Register Abstraction, with its core components of UVM Register Models and the UVM Register Layer, plays a pivotal role in enhancing efficiency and reliability. While it presents certain challenges, such as the need for accurate model design, effective synchronization, and comprehensive coverage, the benefits it brings are substantial.

UVM Register Abstraction saves time and effort, promotes reusability, improves collaboration among team members, and contributes to faster time-to-market. These advantages are invaluable in an industry where competition is fierce, and the demand for reliable, high-performance hardware is unrelenting.

As hardware designs continue to grow in complexity, the use of UVM Register Abstraction is no longer an option but a necessity. Engineers who embrace this approach and master its intricacies are better equipped to navigate the challenges of hardware verification successfully. With UVM Register Abstraction, the journey from design concept to market-ready hardware is not only more efficient but also more assured of success in a rapidly evolving technological landscape.