In the realm of System-on-Chip (SOC) design and validation, efficiency and accuracy are paramount. One critical aspect of this process is the Universal Verification Methodology (UVM) Register Abstraction Layer (RAL), a key component in UVM-based verification environments. In this article, we delve into the significance of automating the UVM RAL for streamlined SOC validation.

Understanding UVM Register Abstraction Layer (RAL)

Before delving into automation, let's grasp the role of the UVM Register Abstraction Layer. The RAL acts as a bridge between the design and verification components of an SOC. It provides a systematic way to model and interact with registers in the design, enabling efficient verification of register-based functionalities.

Challenges in Manual RAL Implementation

Traditionally, engineers have manually crafted RAL models, which can be a time-consuming and error-prone process. Manually coding each register, field, and associated behaviors not only demands significant effort but also introduces the risk of human error. As SOC designs become increasingly complex, the need for automation becomes apparent.

The Automation Advantage

Time and Resource Efficiency: Automation of the UVM RAL dramatically reduces development time. By leveraging automation scripts or tools, engineers can generate RAL models swiftly and accurately, allowing them to focus on more complex aspects of SOC validation.

Consistency Across Projects: Automation ensures consistency in RAL models across different projects. This consistency is crucial for maintaining a standardized and easily maintainable verification environment, especially in organizations with multiple projects and design teams.

Error Reduction: Automated generation minimizes the risk of human errors in RAL models. The precise and systematic nature of automation tools helps eliminate common pitfalls associated with manual coding, leading to more reliable verification environments.

Implementing Automation in UVM RAL

1. Script-Based Automation:

Utilizing scripting languages such as Python or Perl can significantly accelerate the generation of UVM RAL models. Engineers can develop custom scripts tailored to their specific design requirements, automating the repetitive aspects of RAL creation.

2. Template-Based Automation:

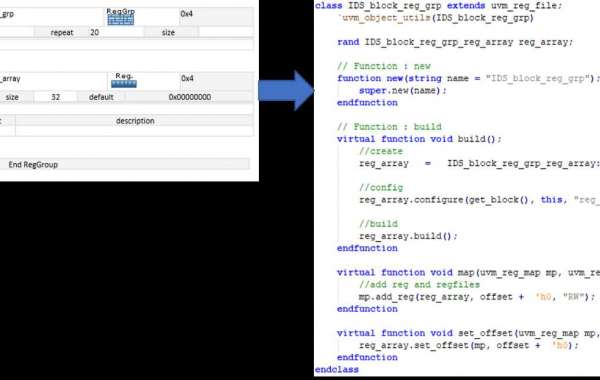

Another approach involves using templates that define the structure of RAL models. By populating these templates with design-specific information, engineers can generate comprehensive RAL models quickly and consistently.

3. Tool-Assisted Automation:

Specialized tools designed for UVM RAL automation offer a more user-friendly approach. These tools often come with intuitive graphical interfaces, allowing engineers to input design specifications and generate RAL models seamlessly.

Realizing the Benefits in SOC Validation

The advantages of automating the UVM RAL extend beyond the initial development phase. During SOC validation, automated RAL models contribute to:

Efficient Testbench Creation: Automated RAL models facilitate the swift creation of testbenches, enabling engineers to focus on designing robust test scenarios rather than grappling with manual RAL implementation.

Scalability Across Verification Environments: Automated RAL generation ensures scalability across different verification environments. As SOC designs evolve, the automated models can adapt, maintaining compatibility with evolving project requirements.

Improved Debugging and Analysis: The systematic nature of automated RAL models enhances debugging and analysis capabilities. Engineers can trace issues back to specific registers and fields more efficiently, expediting the resolution process.

Overcoming Potential Challenges

While the benefits of UVM RAL automation are evident, it's crucial to address potential challenges:

Tool Selection: Choosing the right automation tool is paramount. Engineers should evaluate available tools based on their compatibility with the design flow, ease of use, and support for future updates.

Customization: Projects may have unique requirements that demand customization. Engineers must ensure that the chosen automation approach allows for easy customization without sacrificing efficiency.

Conclusion

Automating the UVM Register Layer is a strategic move towards enhancing SOC validation processes. The time and resource savings, coupled with improved consistency and reduced errors, position automation as a critical enabler for efficient verification environments. As SOC designs continue to evolve, embracing automation in UVM RAL becomes not just a choice but a necessity for staying competitive in the dynamic landscape of semiconductor design and validation.